## Read Margin Check

## Sense-Amp Signal vs Internal Noise

- CharFlo-Memory!<sup>TM</sup> can locate

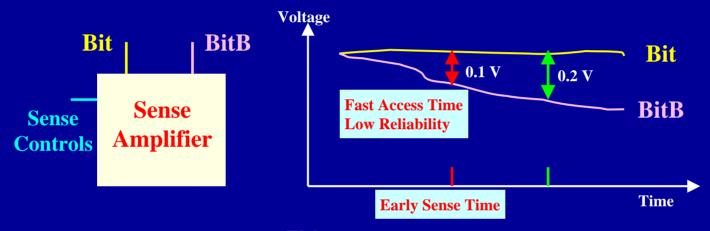

- Bit and BitB signal

- Sense control signal

Any change on voltage supply, .temp, process corners will impact Bit, BitB and Sense Controls.

• CharFlo-Memory!<sup>TM</sup> can automate the simulation output and measurement for reliability check

## Determine Read-Margin Setting

## Checking for Yields and Speed

Determine Read-Margin setting based upon access time,

Voltage(Bit-BitB) against noise-margin

| Read Margin | <b>Access Time</b> | V(Bit-BitB) | SRAM 8Kx24    |

|-------------|--------------------|-------------|---------------|

| 1000        | 4.3212 ns          | 365.8 mv    | Slow          |

| 0100        | 1.8824 ns          | 95.9 mv     |               |

| 1101        | 2.8109 ns          | 200.6 mv    |               |

| 0111        | 1.8824 ns          | 95.9 mv     |               |

| 1111        | 1.6969 ns          | 68.3 mv     | <b>Danger</b> |

<sup>\*</sup> Noise margin is 100 mv minimum normally, and 200 mv for the safer.

Wrong Read Margin (RM) setting causes Poor Yield!